일반적으로 반도체 소자의 개발, 생산 및 사용 과정에서 작은 불량을 피하기는 어렵습니다. 제품 품질 요구 사항이 지속적으로 향상됨에 따라 불량 분석의 중요성이 점점 더 커지고 있습니다. 특정 불량 칩을 분석함으로써 회로 설계자는 소자 설계 결함, 공정 변수 불일치, 주변 회로의 부적합한 설계 또는 해당 문제로 인한 오작동을 발견할 수 있습니다. 반도체 소자 불량 분석의 필요성은 주로 다음과 같은 측면에서 드러납니다.

(1) 고장분석은 소자칩의 고장 메커니즘을 규명하는데 필요한 수단이다.

(2) 고장 분석은 효과적인 고장 진단을 위한 필요한 기초와 정보를 제공합니다.

(3) 고장분석은 설계 엔지니어가 칩 설계를 지속적으로 개선하거나 수리하고 설계 사양에 따라 보다 합리적으로 설계할 수 있도록 필요한 피드백 정보를 제공합니다.

(4) 고장분석은 생산시험에 필요한 보완자료를 제공하고 검증시험 프로세스의 최적화를 위한 필요한 정보기반을 제공할 수 있다.

반도체 다이오드, 오디오 또는 집적 회로의 고장 분석을 위해서는 먼저 전기적 매개변수를 테스트하고, 광학 현미경으로 외관 검사를 한 후 포장을 제거해야 합니다. 칩의 기능 무결성을 유지하면서 내부 및 외부 리드, 본딩 지점, 그리고 칩 표면은 다음 단계의 분석을 준비할 수 있도록 최대한 보존해야 합니다.

주사 전자 현미경과 에너지 스펙트럼을 사용하여 이 분석을 수행합니다. 여기에는 미세 형태 관찰, 고장 지점 탐색, 결함 지점 관찰 및 위치, 소자의 미세 기하학적 크기와 거친 표면 전위 분포의 정확한 측정, 디지털 게이트 회로의 논리적 판단(전압 대비 영상 방법 포함)이 포함됩니다. 에너지 분광기 또는 분광계를 사용하여 이 분석을 수행합니다. 미세 원소 구성 분석, 재료 구조 또는 오염 물질 분석.

01. 반도체 소자의 표면 결함 및 화상

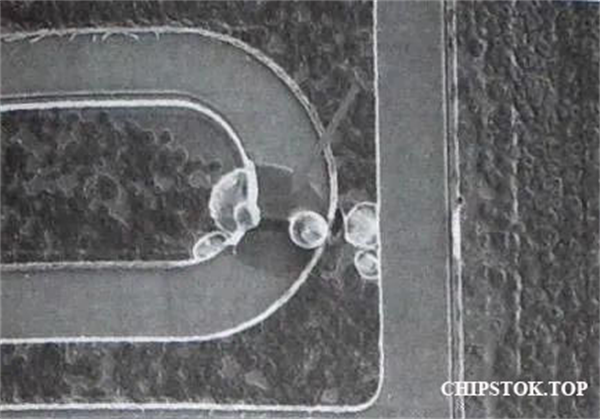

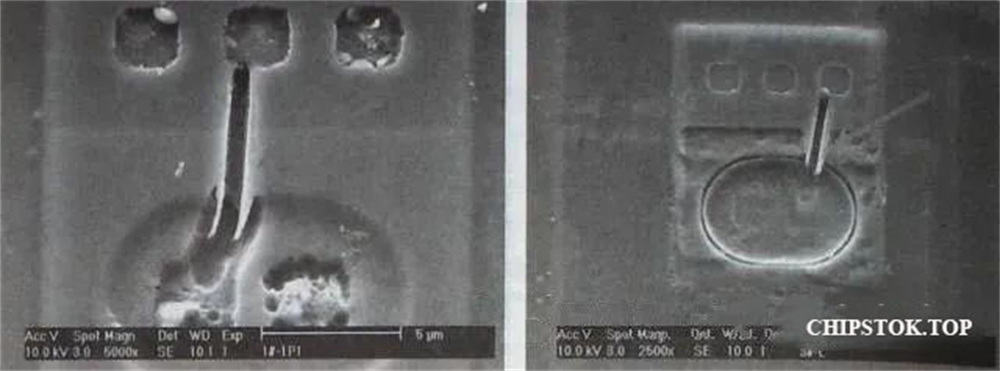

그림 1에서 볼 수 있듯이, 반도체 소자의 표면 결함과 소손은 모두 일반적인 고장 모드이며, 이는 집적 회로의 정제된 층에 결함이 있는 경우입니다.

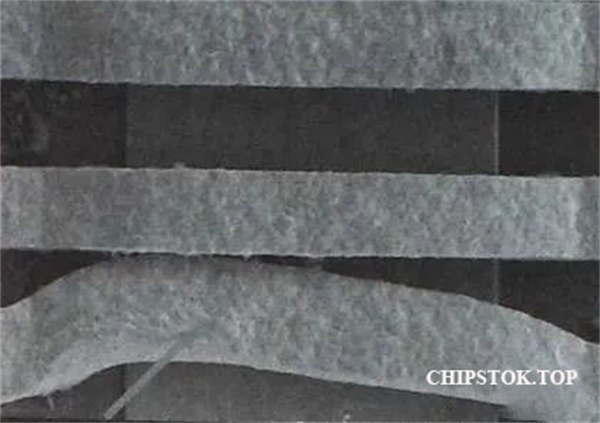

그림 2는 집적회로의 금속화층의 표면 결함을 나타낸다.

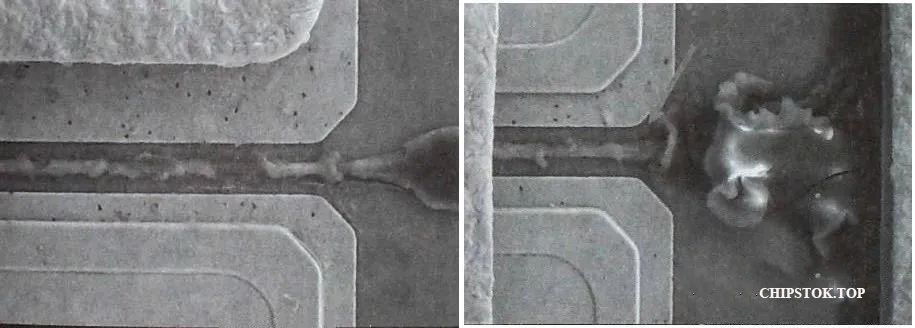

그림 3은 집적 회로의 두 금속 스트립 사이의 파괴 채널을 보여줍니다.

그림 4는 마이크로파 장치의 공기 다리에서 금속 스트립이 붕괴되고 비스듬히 변형되는 모습을 보여줍니다.

그림 5는 마이크로파관의 그리드 소손을 보여줍니다.

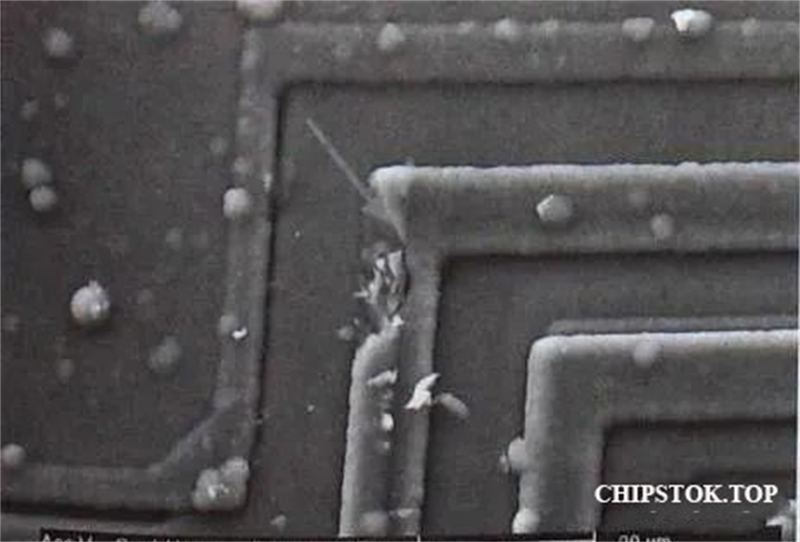

그림 6은 통합된 전기 금속선의 기계적 손상을 보여줍니다.

그림 7은 메사 다이오드 칩의 개방 및 결함을 보여줍니다.

그림 8은 집적 회로의 입력에 있는 보호 다이오드의 파괴를 보여줍니다.

그림 9는 집적회로 칩의 표면이 기계적 충격에 의해 손상되는 모습을 보여준다.

그림 10은 집적 회로 칩의 부분적인 소손을 보여줍니다.

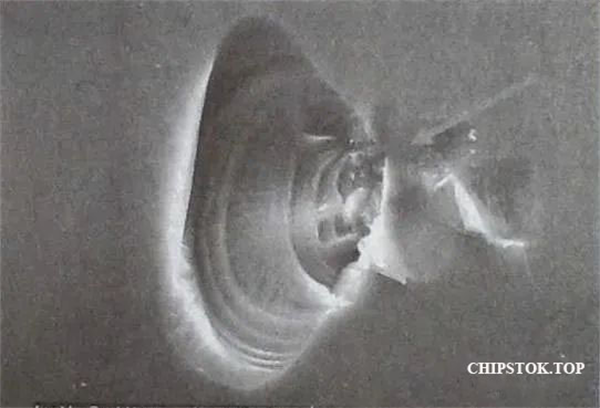

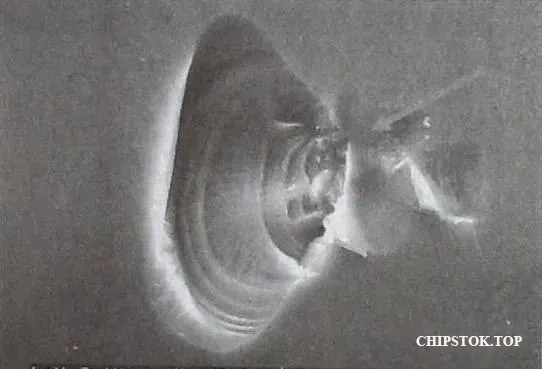

그림 11은 다이오드 칩이 파손되어 심하게 타버렸고, 파손 지점이 녹는 상태로 바뀌었음을 보여줍니다.

그림 12는 질화갈륨 마이크로파 전력관 칩이 연소된 모습을 보여주며, 연소점은 용융 스퍼터링 상태를 나타낸다.

02. 정전기 파괴

반도체 소자는 제조, 패키징, 운송부터 회로 기판 삽입, 용접, 기계 조립 및 기타 공정에 이르기까지 정전기의 위협에 노출됩니다. 이 과정에서 잦은 이동과 외부에서 발생하는 정전기에 쉽게 노출되어 운송 중 손상될 수 있습니다. 따라서 손실을 줄이기 위해 전송 및 운송 중 정전기 보호에 특히 주의해야 합니다.

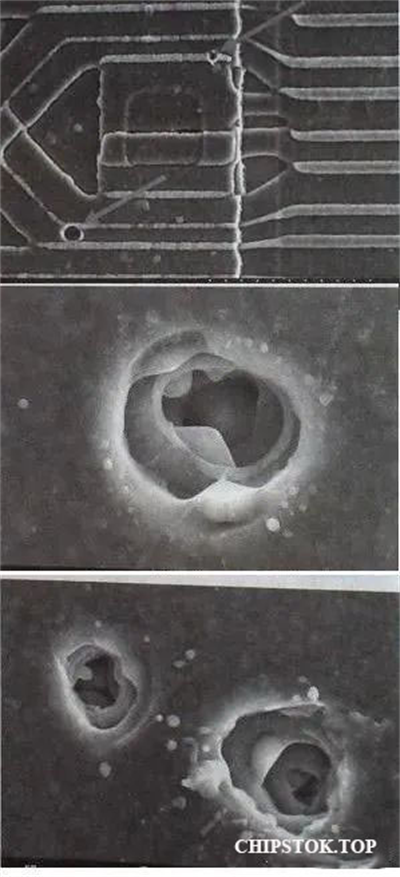

단극성 MOS 튜브와 MOS 집적 회로를 갖춘 반도체 소자는 정전기에 특히 민감하며, 특히 MOS 튜브는 자체 입력 저항이 매우 높고 게이트-소스 전극 커패시턴스가 매우 작아 외부 전자기장이나 정전 유도의 영향을 받아 대전되기 쉽고, 정전기 발생으로 인해 전하를 제때 방전하기 어렵습니다.따라서 정전기가 축적되어 소자의 순간적인 절연 파괴를 일으키기 쉽습니다.정전기 절연 파괴의 형태는 주로 전기적 독창적인 절연 파괴입니다.즉, 그리드의 얇은 산화막이 파괴되어 핀홀을 형성하여 그리드와 소스 또는 그리드와 드레인 사이의 간격을 단락시킵니다.

MOS 집적 회로는 MOS 튜브에 비해 정전 파괴 능력이 상대적으로 약간 더 우수한데, 이는 MOS 집적 회로의 입력 단자에 보호 다이오드가 장착되어 있기 때문입니다. 큰 정전 전압이나 서지 전압이 인가되면 대부분의 보호 다이오드는 접지로 전환될 수 있지만, 전압이 너무 높거나 순간 증폭 전류가 너무 큰 경우, 그림 8과 같이 보호 다이오드가 스스로 방전되는 경우가 있습니다.

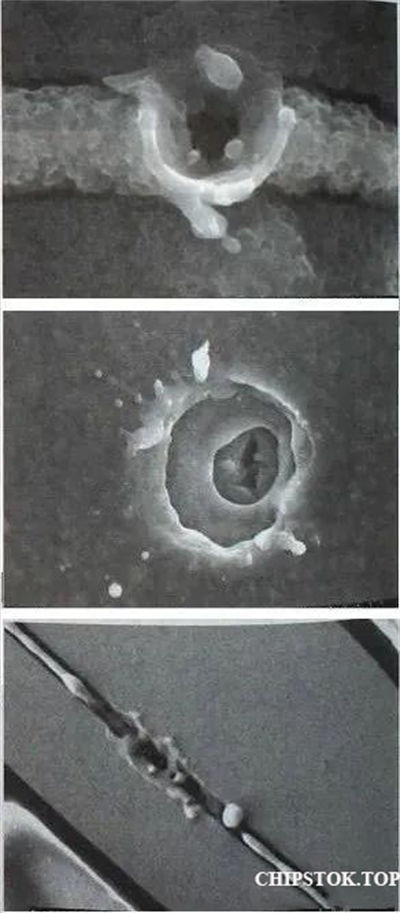

그림 13에 나타난 여러 사진은 MOS 집적 회로의 정전기 파괴 토포그래피를 보여줍니다. 파괴점은 작고 깊으며, 용융 스퍼터링 상태를 나타냅니다.

그림 14는 컴퓨터 하드디스크의 자기헤드의 정전기 파괴 모습을 나타낸 것이다.

게시 시간: 2023년 7월 8일