DIP 이해하기

DIP는 플러그인 방식입니다. 이러한 방식으로 패키징된 칩은 두 줄의 핀을 가지며, DIP 구조의 칩 소켓에 직접 용접하거나 동일한 개수의 구멍을 가진 용접 위치에 용접할 수 있습니다. PCB 기판 천공 용접이 매우 편리하고 마더보드와의 호환성도 우수하지만, 패키징 면적과 두께가 상대적으로 크고, 삽입 및 제거 과정에서 핀이 손상되기 쉽고 신뢰성이 낮습니다.

DIP는 가장 널리 사용되는 플러그인 패키지로, 표준 로직 IC, 메모리 LSI, 마이크로컴퓨터 회로 등에 적용됩니다. SOJ(J형 핀 소형 프로파일 패키지), TSOP(얇은 소형 프로파일 패키지), VSOP(매우 작은 프로파일 패키지), SSOP(축소 SOP), TSSOP(얇은 축소 SOP) 및 SOT(소형 프로파일 트랜지스터), SOIC(소형 프로파일 집적 회로) 등에서 파생된 소형 프로파일 패키지(SOP)도 있습니다.

DIP 소자 조립 설계 결함

PCB 패키지 구멍은 장치보다 큽니다.

PCB 플러그인 홀과 패키지 핀 홀은 사양에 따라 제작됩니다. 제판 과정에서 홀에 구리 도금이 필요하므로 일반적인 허용 오차는 ±0.075mm입니다. PCB 패키징 홀이 실제 소자의 핀보다 너무 크면 소자 풀림, 주석 함량 부족, 공기 용접 등 품질 문제가 발생할 수 있습니다.

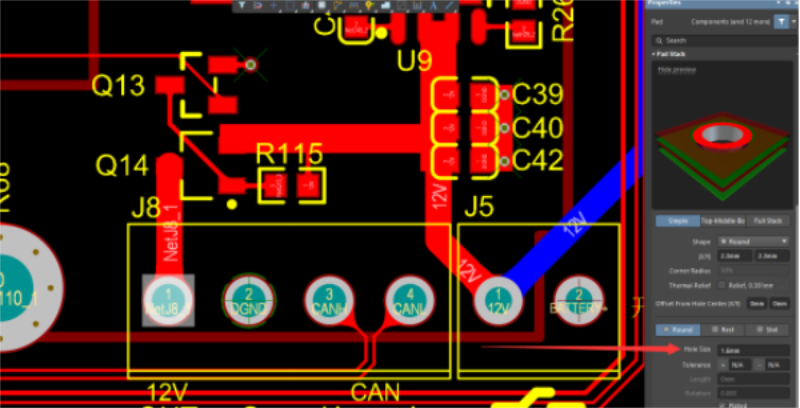

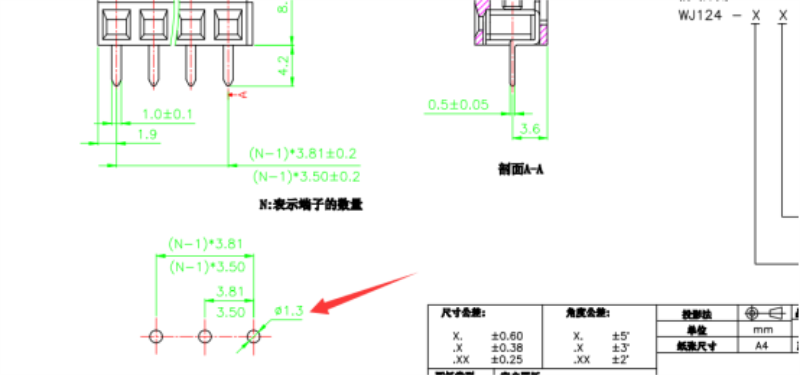

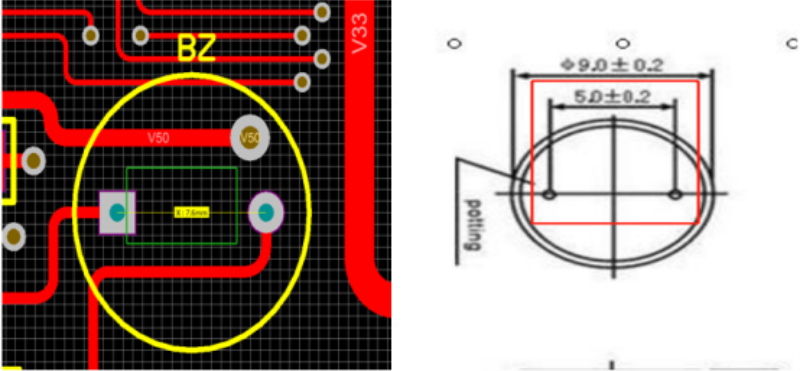

아래 그림을 보면, WJ124-3.81-4P_WJ124-3.81-4P(KANGNEX)를 사용하여 장치 핀은 1.3mm, PCB 패키징 구멍은 1.6mm이며, 조리개가 너무 커서 과파 용접 공간 시간 용접이 발생합니다.

그림에 첨부한 바와 같이, 설계 요구사항에 따라 WJ124-3.81-4P_WJ124-3.81-4P(KANGNEX) 부품을 구매하시면, 핀 1.3mm가 정확합니다.

PCB 패키지 구멍은 장치보다 작습니다.

플러그인 방식이지만 구리에 구멍이 생기지 않습니다. 단일 및 이중 패널인 경우 이 방법을 사용할 수 있으며 단일 및 이중 패널은 바깥쪽으로 전기가 통하고 납땜도 통할 수 있습니다. 다층 기판의 플러그인 구멍은 작고, 내부 층이 전기가 통하는 경우에만 PCB 기판을 다시 만들 수 있습니다. 내부 층의 통전은 리밍으로 복구할 수 없기 때문입니다.

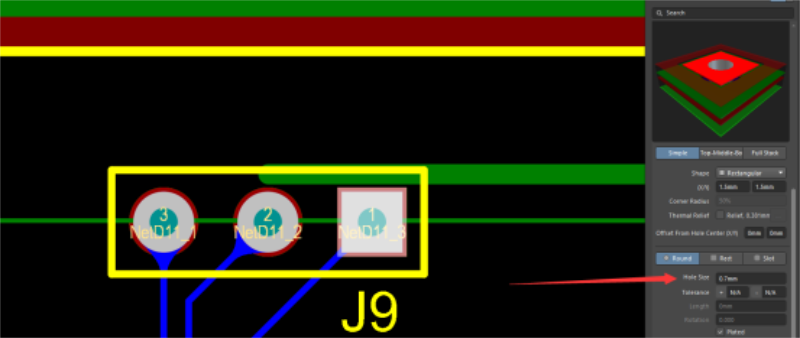

아래 그림과 같이 A2541Hwv-3P_A2541HWV-3P(CJT) 부품을 설계 요구 사항에 맞게 구매했습니다. 핀 직경은 1.0mm이고 PCB 실링 패드 구멍은 0.7mm로 인해 삽입이 실패했습니다.

A2541Hwv-3P_A2541HWV-3P(CJT) 부품은 설계 요구 사항에 따라 구매되었습니다. 핀 직경은 1.0mm가 맞습니다.

패키지 핀 간격은 장치 간격과 다릅니다.

DIP 장치의 PCB 밀봉 패드는 핀과 동일한 개구부를 가질 뿐만 아니라 핀 구멍 사이의 거리도 동일해야 합니다. 핀 구멍과 장치 사이의 간격이 일정하지 않으면, 조정 가능한 발 간격을 가진 부품을 제외하고는 장치를 삽입할 수 없습니다.

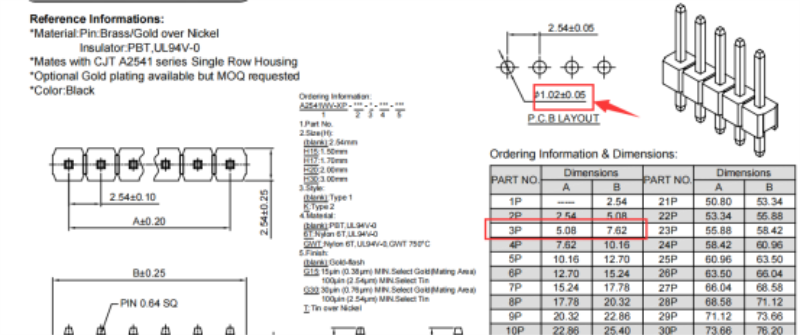

아래 그림과 같이 PCB 패키징의 핀홀 간격은 7.6mm이고, 구매 부품의 핀홀 간격은 5.0mm입니다. 2.6mm의 차이가 발생하면 장치를 사용할 수 없게 됩니다.

PCB 패키징 구멍이 너무 가깝습니다.

PCB 설계, 도면 및 패키징 작업 시 핀홀 간격에 주의를 기울여야 합니다. 베어 플레이트를 제작할 수 있더라도 핀홀 간격이 좁으면 웨이브 솔더링으로 조립하는 동안 주석 단락이 발생하기 쉽습니다.

아래 그림과 같이 핀 간격이 좁으면 단락이 발생할 수 있습니다. 납땜 주석의 단락에는 여러 가지 원인이 있습니다. 설계 단계에서 조립성을 미리 방지할 수 있다면 문제 발생률을 줄일 수 있습니다.

DIP 소자 핀 문제 사례

문제 설명

DIP 제품의 파동봉 용접 후, 네트워크 소켓의 고정 풋의 납땜판에 주석이 심각하게 부족한 것으로 나타났으며, 이는 공기 용접에 속합니다.

문제의 영향

이로 인해 네트워크 소켓과 PCB 보드의 안정성이 나빠지고, 제품 사용 시 신호 핀 풋에 힘이 가해져 결국 신호 핀 풋의 연결이 끊어져 제품 성능에 영향을 미치고 사용자의 사용에 실패할 위험이 있습니다.

문제 확장

네트워크 소켓의 안정성이 낮고, 신호핀의 연결 성능이 좋지 않으며, 품질 문제가 있어 사용자에게 보안 위험을 초래할 수 있으며, 최종 손실은 상상할 수 없습니다.

DIP 소자 조립 분석 점검

DIP 소자 핀과 관련된 문제는 많고, 많은 핵심 사항들이 간과되기 쉬워 결국 폐기되는 경우가 많습니다. 그렇다면 이러한 문제를 어떻게 신속하고 완벽하게 해결할 수 있을까요?

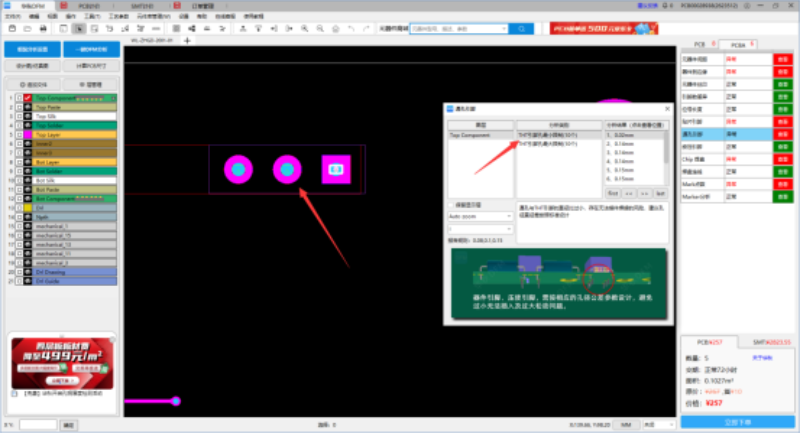

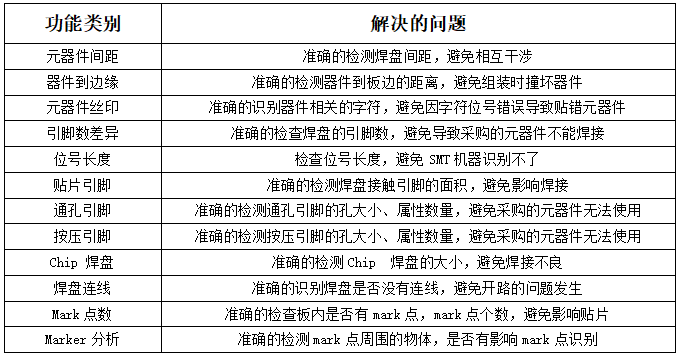

CHIPSTOCK.TOP 소프트웨어의 조립 및 분석 기능을 활용하여 DIP 소자의 핀에 대한 특수 검사를 수행할 수 있습니다. 검사 항목에는 관통 구멍 핀 수, THT 핀의 최대 허용 한계, 최소 허용 한계, 그리고 THT 핀의 속성 등이 포함됩니다. 핀 검사 항목은 기본적으로 DIP 소자 설계 시 발생할 수 있는 문제점을 다룹니다.

PCB 설계가 완료된 후, PCBA 조립 분석 기능을 사용하면 사전에 설계 결함을 발견하고, 생산 전에 설계 이상을 해결하고, 조립 공정의 설계 문제를 방지하고, 생산 시간을 지연시키고, 연구 개발 비용을 낭비하는 것을 방지할 수 있습니다.

조립 분석 기능은 10개의 주요 항목과 234개의 세부 항목 검사 규칙을 갖추고 있어, 장치 분석, 핀 분석, 패드 분석 등 발생 가능한 모든 조립 문제를 포괄하여 엔지니어가 미리 예상할 수 없는 다양한 생산 상황을 해결할 수 있습니다.

게시 시간: 2023년 7월 5일